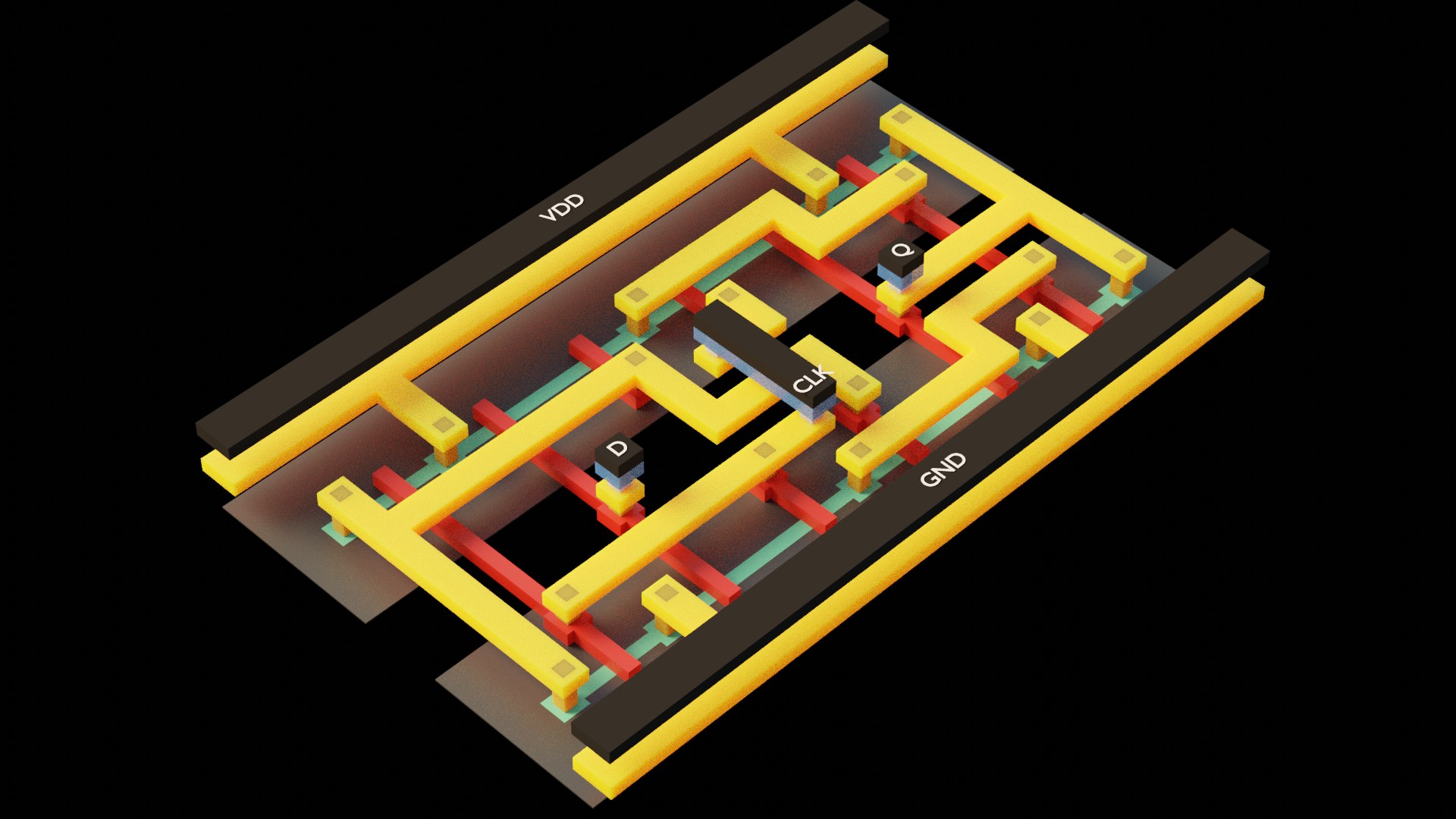

diff --git a/markdowns/index/large_content.md b/markdowns/index/large_content.md index 9d16550f9f69834d3ae04caff98f79a2d03cbf89..973f47813baa4e2a08135306c8d089f102a9ddc2 100644 --- a/markdowns/index/large_content.md +++ b/markdowns/index/large_content.md @@ -38,7 +38,9 @@ In addition to these efforts, we also aim at providing valuable contribution in Standard Cells are the basic building blocks of modern chip-design, they are used to automatically synthesize, place and route digital logic into chips. The synthesis step (e.g. done with yosys) chooses which standard cells should be used to implement the given logic, then the placement step places the cells on a grid, then the routing step connects the standard cells with metal connections for power and signals. At Libresilicon we believe that having many more standard cells will make the overall designs more efficient because the synthesis engine can choose from more cells, therefore we are automating the generation of whole standard cell libraries. -The development of the StdCellLib generator started in 2018, it is currently targeted for LS1U, Sky130 and GF180, and we did successful tapeouts on Sky130 already. Successful tapeouts on Sky130: Link1 Link2 We have prepared a library for GF180 for 5V already but haven’t taped it out yet. + + +The development of the StdCellLib generator started in 2018, it is currently targeted for LS1U, Sky130 and GF180, and we did successful tapeouts on Sky130 already. We have prepared a library for GF180 for 5V already but haven’t taped it out yet. Currently not yet in scope: Pad-Cells, but we hope to do that in the future, once the work on the standard cells is finished.